Workshop on Stochastic COmputing for Neuromorphic Architectures

Artificial Intelligence applications are a major driver in the hardware development of smart systems. An unprecedented number of proposals for better neuromorphic and neuro-inspired hardware architectures have been suggested, ranging from extremely large and high-performance “wafer-scale” circuits to emerging nano-electronic device-based circuits for storing and manipulating information. The proposed workshop looks at neuromorphic hardware from a different perspective: How to provide sufficient AI and ML performance in applications with extremely limited resources like area, power and energy. Among such approaches, stochastic computing promises outstanding area- and power-efficiency because it offers very compact and reliable realizations of the basic arithmetic operations found in a broad range of neuromorphic applications. The workshop SCONA will bring together researchers working on stochastic computing and resource-limited neuromorphic architectures.

Workshop organizers:

John P. Hayes (University of Michigan, Ann Arbor, USA)

Ilia Polian (University of Stuttgart, Germany)

Weikang Qian (Shanghai Jiao Tong University, China)

A special issue of IEEE Design & Test Magazine on the topic of the workshop will appear. There will be a separate call for papers for this special issue; the preliminary deadline is May 1.

https://ieee-ceda.org/call-papers-special-issue-stochastic-computing-neuromorphic-architectures

Final Program

SCONA 2020 Technical Program

Workshop on Stochastic COmputing for Neuromorphic Architectures

Friday, March 13, 2020, ALPEXPO Grenoble

9:00-9:15 Workshop introduction

Ilia Polian1, John P. Hayes2, Weikang Qian3, 1University of Stuttgart, 2University of Michigan, Ann Arbor, 3Shanghai Jiao Tong University

9:15-10:00 Keynote

Stochastic Computing for Machine Learning towards an Intelligent Edge

Warren J. Gross, McGill University, Canada

10:00-10:30 Coffee break

10:30-12:00 Session 1: Stochastic Approaches for Artificial Intelligence

PASCA: PArallel Stochastic Computing based Neural Network Accelerators

Runsheng Wang, Peking University, China

Tsetlin Machine: A New Paradigm for Pervasive AI

Adrian Wheeldon1, Rishad Shafik1, Alex Yakovlev1, Jonathan Edwards1, Ibrahim Haddadi1, Ole-Christoffer Granmo2, 1Newcastle University, UK. 2University of Agder, Norway.

Stochastic Neural Networks: Limits and Opportunities

Florian Neugebauer, University of Stuttgart, Germany

12:00-13:00 Lunch

13:00-14:30 Session 2: Emerging Architectures for Stochastic Computing

Introduction to Dynamic Stochastic Computing

Siting Liu, Jie Han, University of Alberta, Canada

From Unary to Low-Discrepancy: Deterministic Bit-streams Revolutionize Stochastic Computing

Hassan Najafi, University of Lousiana in Lafayette, USA

On the Simulation of Software-Driven Stochastic Computing for Emerging Applications

Sercan Aygun1,2, Ece Olcay Gunes2, 1Yildiz Technical University, Turkey, 2Istanbul Technical University, Turkey

14:30-15:00 Coffee break

15:00-16:30 Session 3: Nanotechnology for Stochastic Computing

Stochastic magnetic devices for cognitive computing

Kaushik Roy, Purdue University, USA

Stochastic learning in CMOS integrated HfO2 based memristive arrays

F. Zahari1, M. K. Mahadevaiah2, E. Perez2, E. Perez-Bosch Quesada2, H. Kohlstedt1, Ch. Wenger2,3, M. Ziegler4, 1Kiel University, Germany, 2IHP, Germany, 3Brandenburg Medical School Theodor Fontane, Germany, 4TU Ilmenau, Germany

Unary Computing Meets ReRAM Crossbar: A Novel Solution for Reliable ReRAM-based Neuromorphic Computing

Weikang Qian, Shanghai Jiao Tong University, Shanghai, China

Workshop Wrap-Up

Call for Papers

The workshop invites submissions on, but not limited to, the following topics:

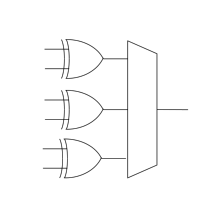

- Stochastic primitives for neural networks and other neuromorphic architectures

- Neuromorphic hardware architectures based on stochastic computing

- Methods for design, synthesis, analysis, and verification of stochastic circuits

- Stochastic circuits and architectures based on emerging technologies

- Applications of neuromorphic stochastic architectures and case studies

The workshop will be co-located with the DATE 2020 conference. At least one author of each accepted paper is expected to register using DATE’s regular registration system. DATE workshops have no formal proceedings but SCONA will prepare an informal electronic proceedings distributed to the workshop participants.

Key dates:

Submission Deadline:

Acceptance Notification:

Final version for workshop proceedings:

January 20, 2020

January 30, 2020

February 15, 2020

Author instructions:

Submissions in form of full 6-page papers or 1-2 page extended abstracts (in IEEE double-column format) should be sent to Ilia Polian by email.

Ilia Polian

Prof. Dr. rer. nat. habil.Head of Institute and Chair of Hardware Oriented Computer Science